TPM

x86 架构首先引入可信平台技术,是基于TPM,TPM 作为一种集成到芯片组中的微控制器,主要用于密钥生成、存储和证书验证,同时保存系统各层次模块的测量值。TPM 基于硬件的密码学特点可以保证存储数据免受外部恶意软件的攻击。

ME

TPM 作为系统子模块由主系统调用,因此与主系统耦合性强,可扩展性弱以及缺乏系统运行行的安全策略。因此Intel于 2007 年推出了ME(management engine)作为嵌入式处理器,采用协处理器和隔离技术。当时,它的主要功能是支持英特尔主动管理技术(AMT),而英特尔AMT是第一个在ME中运行的应用程序。最近,英特尔开始使用 ME 作为可信执行环境 (TEE) 来执行安全敏感型应用程序。

Intel 在主处理器外引入 Quark 芯片 和 MINIX 操作系统,作为单独的子系统运行在用户设备中。ME 子系统拥有独立的物理地址和 IP 地址,通过直接连接网卡访问远程资源,因此管理端可以通过 ME 系统远程透明地管理设备开关机、主系统启动验证、 设备温度、电压等物理特征检测,甚至对主系统运行时状态监控. 由于 ME 子系统拥有独立的计算能力和内存空间,因此在 Intel 架构安全体系中作为基础可信域存在,如主系统其他可信模块的根密钥、证书等均可保存在 ME 系统中,并对证书验证,时钟同步等操作提 供基本的可信执行环境

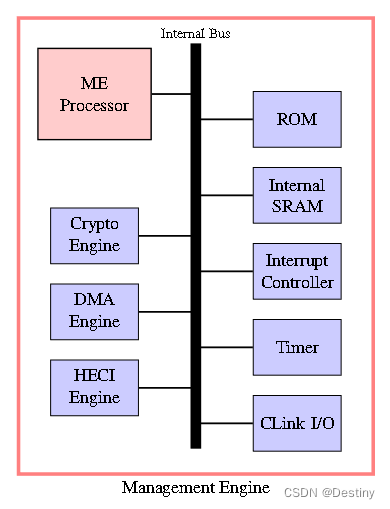

下图展示了ME的硬件架构。从图中我们可以看出,ME就像一台计算机,它包含处理器、加密引擎、直接存储器访问 (DMA)引擎、主机嵌入式通信接口 (HECI) 引擎、只读存储器 (ROM)、内部静态随机存取存储器 (SRAM)、定时器和其他 I/O 设备。ME在处理器上执行指令,并具有代码和数据缓存,以减少对内部SRAM的访问次数。内部SRAM用于存储固件代码和运行时数据。除了内部SRAM之外,ME还使用来自主系统存储器(即主机存储器)的一些动态随机存取存储器(DRAM)。此 DRAM 充当磁盘;ME处理器当前未使用的代码/数据的内存页将从SRAM中逐出,并交换到主机内存中的DRAM中。当系统启动时,BIOS 会保留 DRAM 的区域。此 DRAM 专用于 ME 使用,操作系统无法访问它。但是,ME 的设计不信任 BIOS,它假定主机可以访问保留的 DRAM 区域。

由于嵌入式处理器(即ME处理器)无法对主机内存进行寻址,因此引入了两个引擎(即DAM引擎和HECI引擎)用于ME存储器与主系统内存之间的数据传输。DMA 引擎用于在 ME 内存和主机内存之间移动大量数据。请注意,DMA 引擎在访问主机内存时只能理解物理内存地址。加密引擎用于执行昂贵的加密算法,以便从 ME 处理器卸载换向。密码学引擎包括许多算法,包括 AES、SHA、DRING 和大数算术,ME 固件可以通过调用它们的 API 来使用它们。

SGX

概述

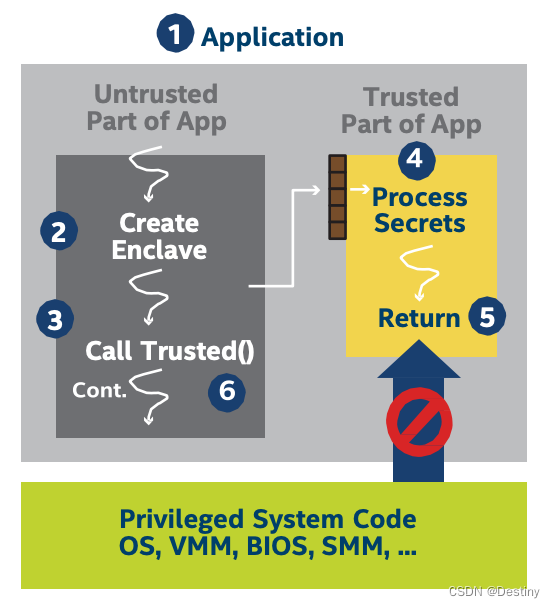

Intel SGX最关键的优势在于将应用程序以外的软件栈如OS和BIOS都排除在了Trusted Computing Base(简称TCB)以外,一旦软件和数据位于Encalve中,即便是操作系统和VMM(Hypervisor)也无法影响Enclave里面的代码和数据,Enclave的安全边界只包含CPU和它本身。

(图片来自:Intel Sgx Product Brief 2019 )

安全执行环境是主机进程的一部分,这意味着:

- 应用程序包含自己的代码、数据和飞地;

- 飞地也包含自己的代码和数据;

- SGX 保护 enclave 代码和数据的机密性和完整性;

- enclave 入口点是在编译期间预先定义的;

- 支持多线程(但正确实现并不简单);

- enclave 可以访问其应用程序的内存,但反之则不行。

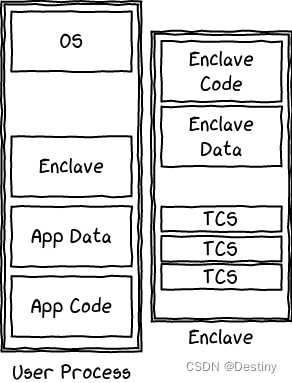

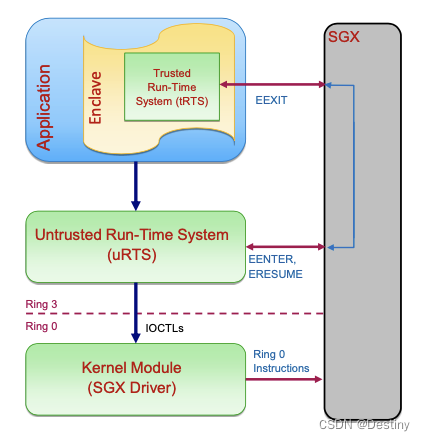

SGX Enclave运行时主要由三个部分组成,分别是运行在Ring0的系统模块即SGX驱动,和运行在Ring3中的非可信运行时系统即uRTS,以及运行在EPC内存区的可信运行时系统(tRTS),其中Enclave代码和数据放置在被称为Enclave Page Cache。

(图片来自:Caslab官网)

SGX驱动主要完成如下工作:

- Enclave加载。

- 内存空间分配与销毁。

- 换页和缺页中断处理。

uRTS主要完成如下工作:

- Enclave加载和卸载。

- 调用管理,处理所有ECall和OCall请求。其中ECall指调用Enclave内的请求,OCall指从Enclave内调用外部的请求。

- 异常处理,判断具体异常反向调用Enclave。

tRTS主要完成如下工作:

- Enclave加载。

- 调用管理,处理ECall和OCall。

相关指令

- ECREATE - 该指令实例化一个新的飞地,定义其地址空间和信任根。这些信息存储在新分配的SECS中。

- EADD - 该指令允许向飞地添加新页面。操作系统全权负责选择页面及其内容。EPCM的初始条目表示页面类型及其保护。

- EEXTEND - 该指令允许按 256 字节块将页面内容添加到 enclave 度量中。必须调用 16 次才能将完整页面添加到度量中。

- EINIT - 该指令在初始化 enclave 之前检查其是否与其EINITTOKEN(相同的度量和属性)相对应。它还检查令牌是否使用Launch Key进行签名。

- EREMOVE - 该指令从 enclave 中永久删除页面。

内存管理

Enclave代码和数据放置在被称为Enclave Page Cache(EPC)的特殊内存区域中,该内存区域使用内存加密引擎(MEE)进行加密,内存总线上的外部读取只能观察到加密数据。仅当页面位于物理处理器核心内时才会被解密。密钥在启动时生成并存储在 CPU 内。

Enclave Page Cache Map (EPCM) 结构用于存储页面状态。它位于受保护的内存内部,其大小限制了EPC的大小(由BIOS设置,最大128MB)。它包含每个页面的配置、权限和类型。

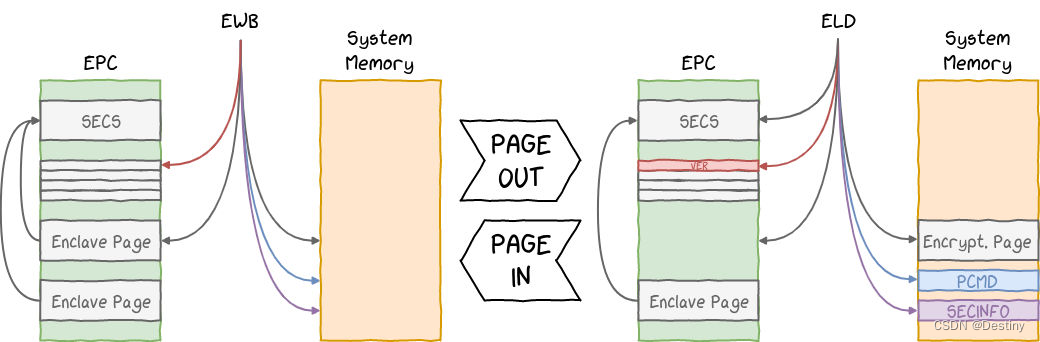

EPC内存由BIOS定义并且大小有限。SGX 有一种方法可以从 EPC 中删除页面,将其放入未受保护的内存中,并在以后恢复。由于 EPC 页面管理指令,页面保持相同的安全属性,允许加密页面并生成额外的元数据。在从所有处理器逻辑核心中删除引用该页的所有高速缓存条目之前,无法删除该页。内容以页面(4KB)为粒度导出或导入。

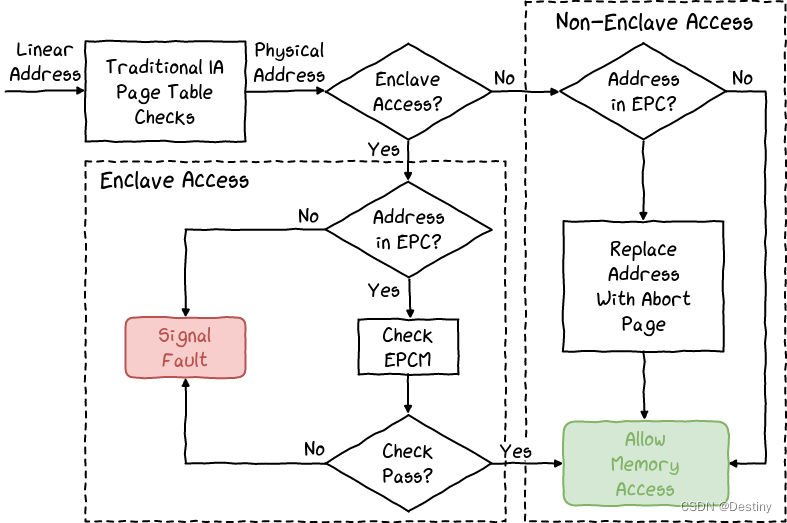

传统的页面检查被扩展以防止外部访问EPC页面。如下图

飞地创建

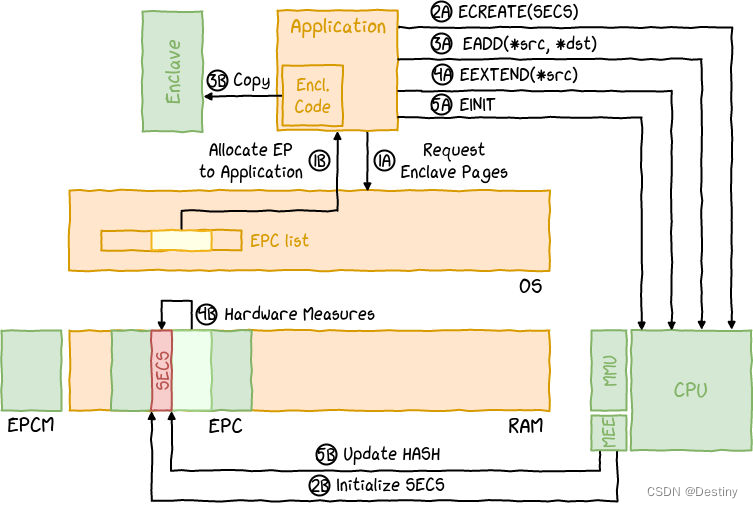

SGX对Enclave内存的保护过程:

- 应用程序请求将其 enclave 加载到内存中;

- ECREATE指令创建并填充SECS结构;

- 使用EADD指令将每个页面加载到受保护的内存中;

- 使用EEXTEND指令将每个页面添加到 enclave 的度量中;

- EINIT指令完成飞地的创建。

(图片来自:Overview of Intel SGX - Part 1, SGX Internals)

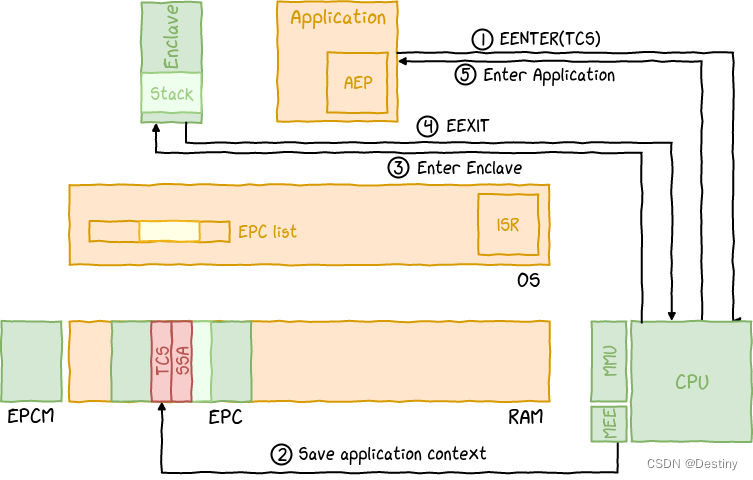

飞地进入、退出EENTER - 该指令将控制从应用程序转移到飞地内的预定位置。它检查TCS是否空闲并清除 TLB 条目。然后,它将处理器置于 enclave 模式并保存RSP / RBP和XCR0寄存器。最后,它禁用基于精确事件的采样( PEBS ),以使飞地执行显示为一条巨型指令。EEXIT - 该指令将进程恢复到其原始模式,并清除位于 enclave 内地址的 TLB 条目。控制权被转移到位于应用程序内并在RBX寄存器中指定的地址,并且TCS结构被释放。enclave需要在退出前清除其寄存器以防止数据泄漏。

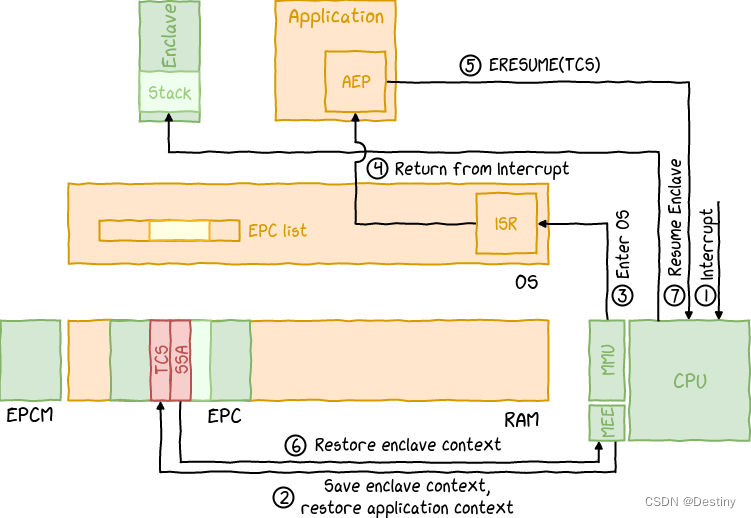

中断处理

- 中断或异常到达处理器;

- enclave上下文被保存,应用程序上下文被恢复;

- 在操作系统的处理程序中继续执行;

- 处理程序将 ( IRET ) 返回给AEP;

- 如果AEP决定恢复 enclave 执行,则执行ERESUME ;

- 之前保存的enclave上下文被恢复;

- 执行从飞地内停止的地方恢复。

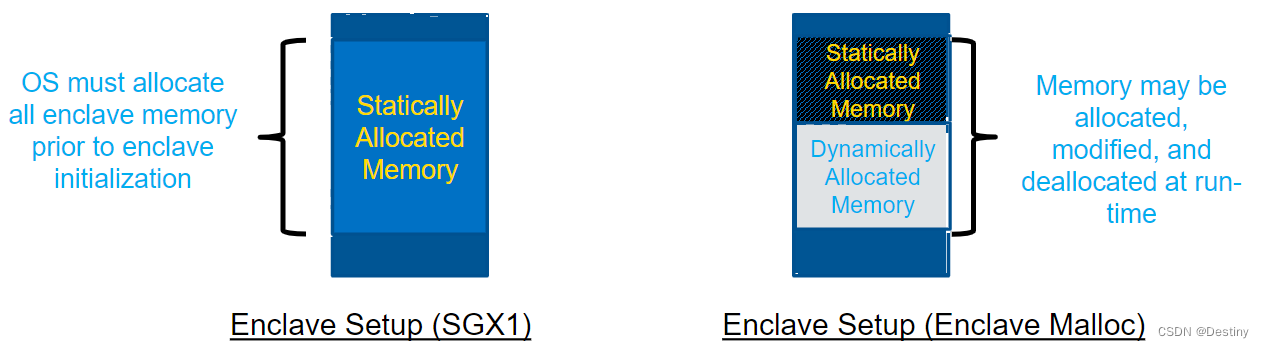

SGX2

Intel SGX已经先后发布了SGX1与SGX2两代次。其中在服务端芯片中SGX2已在2021正式开始大规模商用。

SGX2相较于SGX1增加了Enclave动态内存管理(Enclave Dynamic Memory Management,简称为EDMM)能力。在SGX1的指令集中,创建Enclave时需要提前确认Enclave需要用到的内存大小。并且在运行过程中代码模块不能动态加载到Enclave中。这种设计一是增加了Enclave的启动时间,因为需要确认所有内存地址。二是限制了EPC的空间大小,因为需要预分配,考虑到合理性,SGX1 EPC内存上限被设置为256M。这就导致了在运行过程中超过256M的堆栈,会被以换页的形式加密换出到系统内存中,类似换页就会带来较大的性能开销。

使用 SGX2,可以修改属于 enclave 的常规 enclave 页面的权限,支持将常规 enclave 页面动态添加到 enclave,支持从 enclave 中删除页面,以及扩展 enclave 以允许更多线程。所有这些都是 Software Guard Extensions 的有用补充。SGX2 的功能主要围绕 Enclave 的扩展页面处理,因此也称为 Enclave 动态内存管理 (EDMM)。

SGX2设计引入了EDMM机制,提供了在保证安全性的同时可动态扩缩Enclave内存的能力。EDMM方案中EPC中内存的分配主要有基于OCall事件触发的分配以及基于缺页终端触发的分配两种模式。其核心都是由SGX Driver分配内存页,再由Enclave确认分配生效,分配机制对应用层透明。

SGX2在引入EDMM后,安全性没有降低。SGX2依旧确保Enclave内存页的一致性,一致性可以被度量。由于内存分配依赖OS,为了防止OS提供错误的内存页,每一次内存调整Enclave都需要二次检查内存页(包括权限)的正确性。

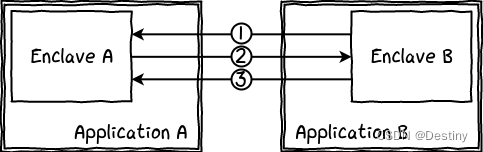

SGX支持通过安全认证技术来向挑战者证明Enclave中运行的用户程序的完整性和真实性。SGX的安全认证分为本地认证和远程认证

本地证明

- enclave A 和 enclave B 之间必须已经建立了通道。enclave A 使用它来检索B 的MRENCLAVE 。

- Enclave A使用B 的MRENCLAVE调用EREPORT,为后者生成签名报告。

- Enclave B 调用EGETKEY来检索其报告密钥并验证EREPORT结构的 MAC 。如果有效,则该飞地是预期的并在合法平台上运行。

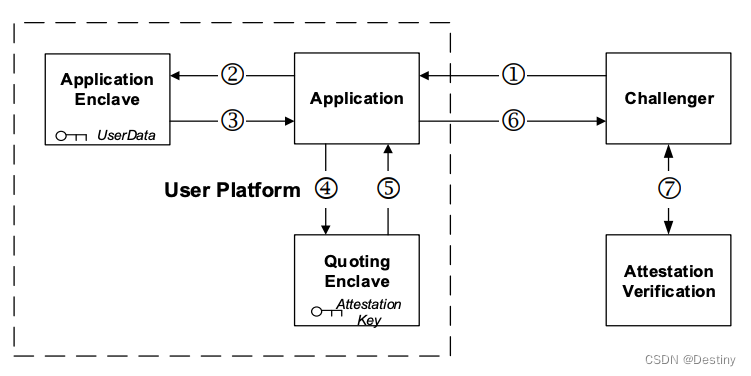

远程认证

远程证明需要一个称为引用飞地( QE ) 的架构飞地。该飞地通过使用另一个特殊密钥(即配置密钥)对REPORT(本地可验证)进行签名来验证并将其转换为QUOTE (可远程验证) 。

- 最初,飞地通知应用程序它需要位于平台外部的秘密。应用程序与服务器建立安全通信。服务器响应质询,以证明 enclave 的执行未被篡改,并且其执行的平台是合法的;

- 应用程序给出引用飞地的身份和对其飞地的挑战;

- Enclave 生成一个清单,其中包括质询答案和一个临时公钥,稍后将使用该密钥来保护服务器和 Enclave 之间的通信。它生成清单的哈希值,并将其包含在EREPORT指令的用户数据部分中。该指令为引用飞地生成一个报告,将清单与飞地联系起来。enclave 将REPORT传递给应用程序。

- 应用程序将报告传输到报价飞地进行验证和签名。

- QE使用EGETKEY指令检索其报告密钥并验证REPORT。它创建QUOTE结构并使用其配置密钥对其进行签名,然后将其返回给应用程序。

- 应用程序将QUOTE和关联的清单发送到服务器以进行验证。

- 服务器使用Intel提供的证明服务来验证QUOTE签名。然后,它使用QUOTE用户数据中的哈希值检查清单完整性。最后,它确保清单包含挑战的预期答案。

(图片来自:Intel Software Guard Extensions EPID Provisioning and Attestation Services)

外界互动

SGX enclave 可以被视为一个能够执行任何任意算法的黑匣子。该黑匣子可以使用下面介绍的三种不同方式与外界进行通信。

- Enclave 调用 (ECALL):应用程序可以调用 enclave 内的预定义函数,将输入参数和指针传递到应用程序内的共享内存。从应用程序到 enclave 的那些调用称为ECALL。

- OCALL:当 enclave 执行时,它可以对应用程序中的预定义函数执行OCALL 。与ECALL相反,OCALL无法与应用程序共享 enclave 内存,因此它必须在OCALL之前将参数复制到应用程序内存中。

- 异步退出 (AEX):由于中断或异常,执行也可能退出飞地。这些 enclave 退出事件称为异步退出事件( AEX )。他们可以从飞地内的任意点将控制权从飞地转移到应用程序。

平台软件

平台软件( PSW ) 是允许支持 SGX 的应用程序在目标平台上执行的软件堆栈。它可用于 Windows 和 Linux 操作系统,由 4 个主要部分组成:

- 提供对硬件功能的访问的驱动程序;

- 多个执行和证明支持库;

- 环境运行所需的架构飞地;

- 加载 enclave 并与 enclave 通信的服务。

参考资料

https://caslab.csl.yale.edu/workshops/hasp2016/HASP16-16_slides.pdf

https://blog.quarkslab.com/tag/trusted-execution-environment.html

TME

TME是Total Memory Encryption的缩写。该架构定义并实现了透明全内存加密特性的最基本功能:使用由处理器内的RNG生成的单一的临时密钥对全部物理内存(包括NVRAM)以透明地方式进行加密。 所谓“临时”指的是每次处理器启动时都会通过RNG重新生成一把密钥,这把密钥被称为平台密钥。一旦开启TME特性,TME exclusion区域以外的全部内存区域全都使用平台密钥进行加解密。

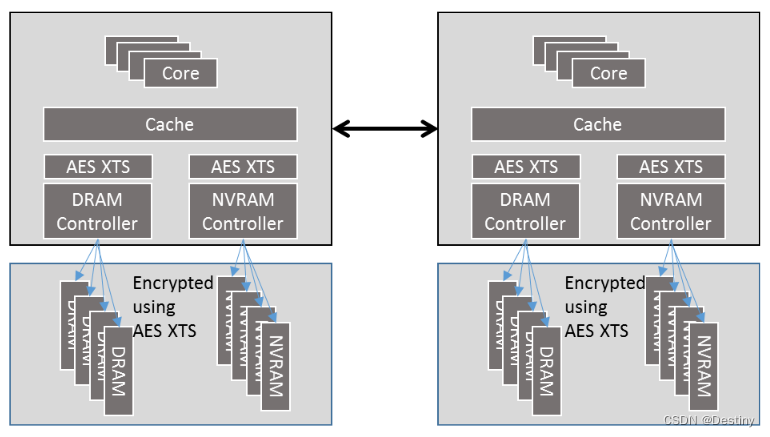

为了防止平台密钥的泄露,软件或处理器接口都无法访问到这把平台密钥。下图是TME架构在一个具有双NUMA节点系统中的参考实现图:

CPU每次在启动时,都会随机生成NIST标准的AES-XTS加密算法用到的秘钥(128bit),这个秘钥临时存在内存控制器中,掉电就会消失,而且为了安全,不能被外界获取。每次总线送过来数据存储时,就用AES-XTS自动加密,再放在内存条中;如果是读取,从内存条中取出来后,用AES-XTS算法解密后再送出去。由于这一切都是在内存控制器IP中自动发生的,外部IP并不知道发生了什么,它们只看到数据进去,然后同样的数据又可以读出来。外部IP可以是带内的CPU、Cache Agent、QPI Agent或者是带外的设备,这样好多过去可以工作的技术可以叠加在TME上工作,包括已有的SGX,兼容性十分好。

总体而言,TME架构具有以下特点:

- 架构和功能简单直接:使用单一的平台密钥对内存进行加密

- 一些更复杂的安全特性(比如SGX2和TDX)可以轻易地叠加在这个基础架构之上

- 对软件几乎完全透明,兼容性好

- 对性能的影响与工作负载强相关

TME的最大缺点是只能使用一把平台密钥来加密内存,不支持在系统里划分出多个基于加密密钥构建的加密内存domain;但MKTME就支持使用多把密钥,进而实现per进程/容器/VM粒度的加密内存domain。

MKTME

MKTME是Multi-Key Total Memory Encryption的缩写。它在TME架构的基础上,实现了以页为粒度、支持使用多把密钥对内存进行加密的功能,同时还允许由软件设置AES-XTS加解密引擎所使用的密钥。

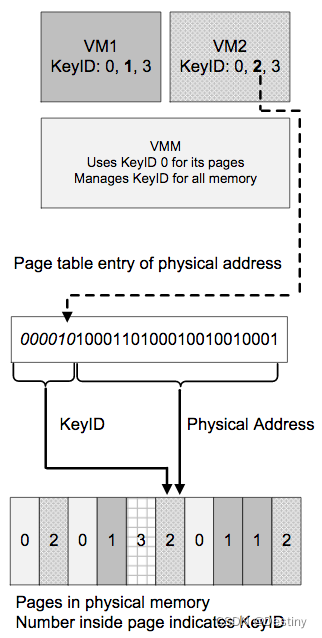

下图是将MKTME用在虚拟化场景中的一个示例图:

在这个示例中:

- Hypervisor使用KeyID 0 (即TME定义的平台密钥)来访问所有的加密内存

- VM1和VM2都可以使用KeyID 0来访问自己的加密内存

- VM1使用KeyID 1来访问自己的私有加密内存

- VM2使用KeyID 2来访问自己的私有加密内存

- VM1和VM2可以使用KeyID 3来访问两个VM共享的加密内存

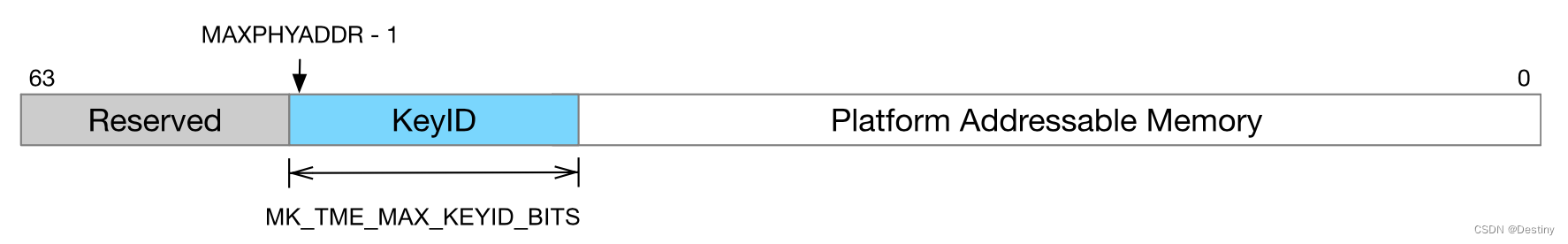

KeyID字段被包含在PTE中,且位于物理地址字段的高位,就像是物理地址字段的一部分(即通过减少一部分物理地址宽度来实现),同时被用在处理器内部的微架构层中(除了AES-XTS引擎),这个特性叫做物理地址位超卖(oversubscribing)。该特性使物理地址具有了别名,即具有相同物理地址的页可以有不同的KeyID。

KeyID信息是不会出现在处理器外部的(比如内存总线上)。物理地址位超卖不会影响cache和TLB的行为,因为KeyID仅被当做成物理地址的一部分来处理;但物理地址位超卖会影响大多数的页表类型:Host普通IA页表、EPT和IOMMU页表。

虽然前面的例子中Hypervisor使用的是KeyID 0,但Hypervisor具有特权,可以使用任意KeyID访问自己的加密内存,也能管理和设置每个VM所能使用的KeyID。

MKTME支持的密钥数量总是固定的,而具体数量由特定的处理器实现来决定。软件可以通过配置只使用其中的部分密钥,这组密钥被称为可用密钥。软件负责管理可用密钥,并可以使用可用密钥对任意一个内存页进行加密。

在软件不进行任何显式配置的情况下,MKTME引擎默认使用TME的平台密钥进行内存加密。MKTME也允许使用软件提供的密钥或处理器RNG生成的密钥。 在虚拟化场景中,VMM或Hypervisor负责管理每个VM所使用的密钥,并透明地对Guest OS实施加密保护(在这个场景中,可以将MKTME视为TME虚拟化技术)。

MKTME的功能

- AES XTS引擎

- 支持多把密钥

- 以页为粒度管理密钥

- 对部分软件透明

- 性能(工作负载相关)

- 支持软件设置和管理密钥

- KeyId字段包含在PET中

- IA paging

- PTE paging

- Iommu paging

- 其他内存结构

TME 和 MKTME 的安全性依赖于特权软件(OS 和 VMM/Hypervisor),这点与传统虚拟化技术的安全边界完全一致。 假设在攻击者拥有特权的情况下,攻击者能将所有物理页的加密模式都改为非加密模式。事实上只要攻击者拥有特权,就已经能够访问任意内存了,只不过需要使用正确的 KeyID 来访问 per 进程/容器/VM 实例的加密内存,比如在访问 VM 实例内的数据前需要在 EPT PTE 中找出正确的 KeyID,然后建立一个使用该 KeyID 的 PTE 映射来访问该物理页。

此外,TME 和 MKTME 没有对数据提供完整性保护,因此软件使用错误的 KeyID 访问加密内存、或直接篡改加密内存中的内容都是可行的(比如纯粹的破坏数据的行为,或是用已知明文的密文来覆盖以实施重放攻击)。

由于特权软件仍有足够的权限来降低 TME 和 MKTME 的安全性,因此 TME/MKTME 技术目前还不属于机密计算的范畴,即无法做到哪怕在被攻破的 OS/VMM 环境里也能够保护租户机密数据的强度。

参考文献:

https://developer.aliyun.com/article/767095

https://en.wikichip.org/wiki/x86/tme?spm=a2c6h.12873639.article-detail.7.6f0273c1XuslWF

https://schd.ws/hosted_files/lc32018/38/mktme_lc3_2018.pdf?spm=a2c6h.12873639.article-detail.10.6f0273c1XuslWF&file=mktme_lc3_2018.pdf

TDX

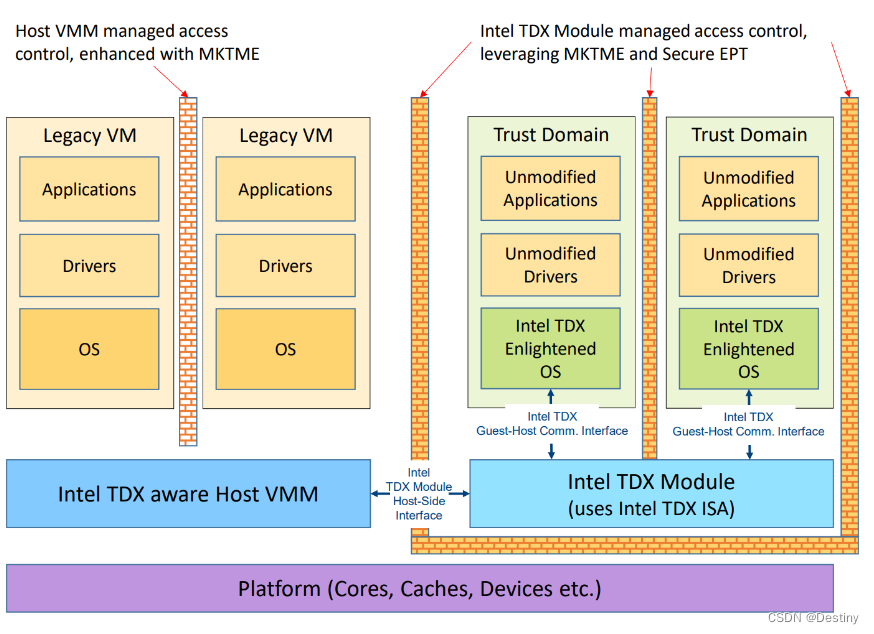

Intel Trust Domain Extensions (Intel TDX) 其实是一套软硬件结合的解决方案,包含很多组件:VMX指令集扩展、MKTME技术、CPU attestation模型、软件集合: TXD module / Intel authenticated code module / Intel quoting enclave。

通过Intel TDX提供的功能,可以构造出区别于传统VM的TD(Trusted Domain):将机密虚拟机和非机密域软件栈(包括hypervisor,VMM和其他非可信域软件栈)隔离,保证机密虚拟机的数据不被非机密域软件获取和篡改。

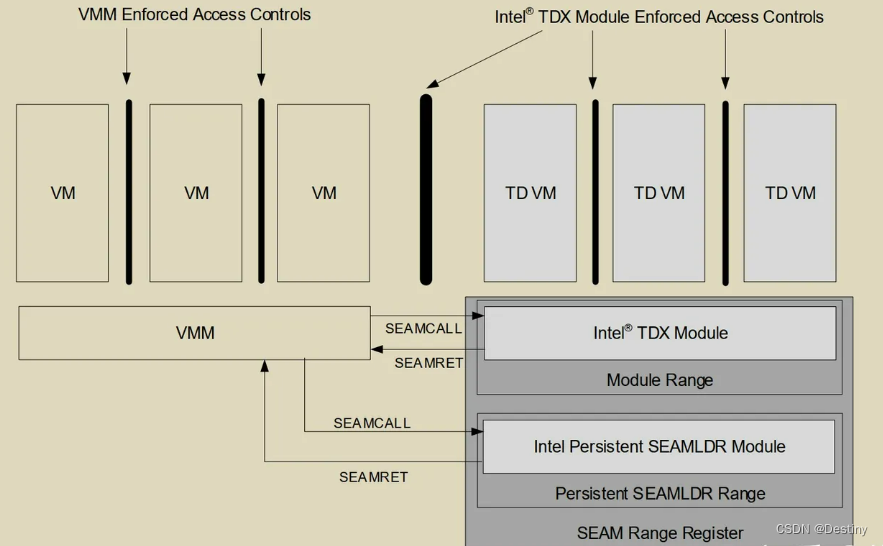

SEAM特权级

Intel TDX 引入 SEAM(Secure Arbitration Mode)特权模式,SEAM 特权模式中包含两种特权级:SEAM VMX root 和 SEAM VMX non-root。

SEAM VMX root特权级中运行两种模块:Intel Persistent SEAMLDR Module 和 Intel TDX Module 和 Intel Persistent SEAMLDR Module。Intel Persistent SEAMLDR Module 负责CPU验证和加载更新Intel TDX Module。Intel TDX Module负责管理虚拟机生命周期(创建、执行和销毁)。由Intel TDX Module拉起的虚拟机运行在SEAM VMX non-root特权级,称为TD VM(Trust Domain VM)。

TD运行在SEAM的non-root模式下,TDX module运行在SEAM的root模式下,通过调用SEAM call可以让CPU进入SEAM root模式,并且加载TDX module。当CPU处于VMX Root特权级时,执行SEAMCALL指令切换到SEAM VMX Root特权级。当RAX寄存器的最高位为1时,CPU切换到Intel P-SEAMLDR module上下文;为0时,CPU切换到TDX-module。SEAMCALL指令保证同一时刻只能有一个物理CPU进入Intel P-SEAMLDR module上下文。

数据加密

Intel TDX模块使用Intel MKTME技术对数据进行加密和完整性保护,一个TD对应一个KeyID,分配给TD的KeyID无法被不可信软件访问。MKTME为TDX预留了一部分可配置的KeyID,这部分KeyID只能在SEAM中使用。

MKTME支持完整性保护。当使能完整性保护时,MKTME将消息认证码(MAC)与每个cache line关联起来。当CPU使用KeyID读取cacheline时,如果存储在元数据中的MAC与MKTME重新生成的MAC不匹配,访问被阻止。

SEAM中可以使用PCONFIG指令为TDX配置私有KeyID。

TDX module

TDX module是一个Intel提供的,使用动态签名机制的,CPU attestation的安全加固模型,TDX module有以下功能:

- 向VMM提供接口,用来创建/销毁/执行TD,解决特权级应用的问题

- CPU/内存保护attestation

- TD密钥的申请和管理

- 减少攻击面

TDX 通过对VMM访问TD的限制或者监控,来保证TD运行过程中的安全,主要包括两个方面的操作:

- TDX module能够保证在运行过程中,拦截不受信的软件(比如VMM)对TD资源的访问,比如CPU控制寄存器,MSR寄存器,调试寄存器,性能监控寄存器,时间戳寄存器等

- TD创建的时候可以选择是否授权TD使用调试和性能监控功能,如果允许的话方可使用,同时,TD attestation report时,也会将这些行为进行report

VMCS

每个TD VM都与一个VMCS关联,VMCS管理和控制SEAM VMX Non-Root执行行为。Intel TDX为SEAM VMX Non-Root的VMCS新增控制域 :

- shared EPT Point:指定共享EPT指针。原先的EPTP控制域用于记录私有EPT地址。

- TD Key identifier:一个32位执行控制字段,指定MKTME KeyID。CPU使用KeyID访问EPTP指向的物理内存地址空间。

- Guest Physical Address Width (GPAW): 指定GPA宽度,内存翻译时使用4级页表还是5级页表。GPA空间被划分为两部分:共享GPA地址空间和私有GPA地址空间。当GPAW.SHARED比特位为0时,指针指向的GPA范围是TD的私有内存,CPU使用TD-KeyID访存,使用EPTP完成内存地址翻译;当GPAW.SHARED比特位为1时,指针指向的GPA范围是TD的共享内存,CPU使用共享KeyID访存。

参考文献

https://zhuanlan.zhihu.com/p/657392420

https://blog.csdn.net/include_IT_dog/article/details/127813289

转载请注明来源,欢迎对文章中的引用来源进行考证,欢迎指出任何有错误或不够清晰的表达,可以在下面评论区评论