https://ieeexplore.ieee.org/abstract/document/9453841

侧信道分析(SCA)攻击是对加密设备的强大威胁,因为它们利用了与其物理行为相关的内部敏感信息[1],[2]。

低级缓存(例如嵌入式存储器)在许多VLSI片上系统(SoC)[13]的面积和功耗中占主导地位,并且是许多加密系统的关键组件,例如智能卡[14]和采用加密算法的无线网络[15],用于存储指令代码和数据。因此,安全嵌入式存储器的分析和设计至关重要。大多数系统的主流嵌入式存储器解决方案基于 6 晶体管 (6T) SRAM 宏单元。然而,传统的6T SRAM单元容易受到电源/电磁分析攻击,因为它们会泄漏敏感信息,这是由于从存储器电源汲取的电流与其存储的数据之间的相关性[8],[9],[16],[17]。

安全静态随机存取存储器 (SRAM) 有助于实现安全目的:它们可以实例化为信任根的一部分,用于存储或引导加载系统、中间计算(L0、L1 缓存、寄存器文件、FIFO 等),或用于存储长期机密(片上 SRAM 宏)。它们还被用作构建基元来构建安全基元,例如 P/T-RNG、存储或加载种子和 SRAM-PUF。

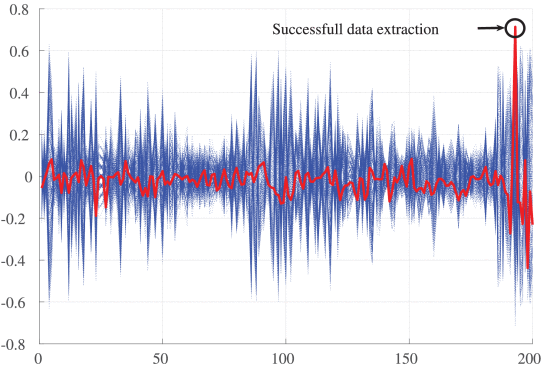

在本文中,我们首先演示了如何使用PA攻击算法成功提取存储在传统6T SRAM宏中的数据,该算法利用了存储器内容与其电源电压[10]电流之间的相关性。这驳斥了常见的误解,即算法噪声或大型内存活动可以击退此类攻击。

我们提出了一种安全的SRAM实现方案,该方案具有一种新型阻抗随机化单元,与传统的SRAM阵列相比,该单元可显著减少信息泄漏[10]。

Side-Channel Attack Resilient Design of a 10T SRAM Cell in 7nm FinFET Technology

集成电路的非侵入性侧信道攻击 (SCA) 多年来一直是一个令人担忧的问题,而漏电功率分析 (LPA) 是 IC 安全的主要威胁之一。对于SRAM模块,LPA将利用存储单元中的数据与其相应的泄漏功率之间的相关性,并可能解密加密系统内存中的密钥。包含敏感消息的SRAM存储器将受到LPA攻击的严重影响。已经提出了几种内存架构来缓解这个问题。

本文基于最近的低功耗单端9T单元设计,提出了一种新的针对LPA的SRAM设计。讨论了9T电池的泄漏平衡问题,并提出了一种新的电池设计。仿真结果证实,所提出的SRAM单元保留了9T设计的优势,并具有均衡的泄漏行为,可防止SCA。

Location, Location, Location: Revisiting Modeling and Exploitation for Location-Based Side Channel Leakages

Sugawara等[48]的工作证明了ASIC中存在基于位置的泄漏。特别是,它们表明芯片SRAM的功耗传达了有关正在访问的存储器地址的信息。他们将这种效应称为“几何”泄漏,因为它与内存布局有关。

Andrikos等[2]使用ARM Cortex-M4的SRAM上显示的基于EM的位置泄漏进行了初步分析。

Schlösser等[40]使用光子侧信道来恢复在激活AES Sbox查找表期间访问的确切SRAM位置。这种位置信息可以帮助密钥恢复,因此即使是光子发射分析的情况也可以归类为基于位置的泄漏。

在我们的工作中,地址泄漏意味着寻址机制的泄漏,例如存储单元控制逻辑的泄漏。这种泄漏甚至可以在远离存储单元本身的地方观察到,例如在内存总线或 CPU 上。位置泄漏是指由这种地址泄漏和单元本身的泄漏引起的泄漏,这通常在它附近观察到。我们将后者称为“空间泄漏”,即位置泄漏同时包含了与地址相关的效应和空间效应。例如,访问内存中的表需要在 CPU 中进行索引和内存寻址(地址泄漏)。此外,访问会导致内存本身被激活(空间泄漏)。对手通常能够观察到这两种类型的泄漏,并且通常很难区分它们。

1.我们提供了一个简单的模型来捕捉空间泄漏的影响。该模型的动机是在 ARM Cortex-M4 的 SRAM 中观察到的实验数据。

2.利用新建立的模型,我们模拟了增强或减少空间泄漏的不同理论场景。我们使用感知信息 (PI) 指标调查每个场景的安全性。

3.我们使用均值差分、多变量模板攻击和神经网络对现代 ARM Cortex-M4 的 SRAM 进行了首次基于位置的实际攻击。

4.我们展示了可以区分每个 128 字节的连续 SRAM 区域(成功率为 100%)和区分 256 个连续 SRAM 字节(成功率为 32%)的攻击。我们得出的结论是,基于EM位置的泄漏足以危及使用SRAM查找表的AES实现的安全性。

Leakage Power Attack-Resilient Symmetrical 8T SRAM Cell

传统的SRAM单元容易受到侧沟道漏电功率攻击。为了提供对这些类型攻击的弹性,我们提出了一种对称的8T SRAM单元,它比传统的6T单元多包含两个晶体管,以显着降低存储数据与泄漏电流之间的相关性。

对传统6T SRAM单元进行LPA攻击的主要机制是单元在保持模式下的不对称泄漏电流,具体取决于存储的数据和BL/BLB电压。为了避免这种不对称性,并为两个数据电平产生类似的待机电流模式,我们提出了一种8T SRAM单元实现,以前用于提高读取速度[16]。

在6T SRAM阵列上展示了泄漏电源攻击,并通过泄漏电流测量成功提取了数据,证明了其对安全应用的不可靠性。

Evaluation of fault attack detection on SRAM-based FPGAs

本文介绍的工作是双重的。首先,我们提出了基于SRAM的FPGA故障检测机制的概念,该机制基于功能模块的冗余,这些模块将均匀地放置在FPGA平面图上,并组成故障检测网格。在下文中,我们介绍了基于SRAM的FPGA的配置存储器中的故障注入结果,该FPGA用于评估该检测模块的不同配置的检测能力。为此,故障注入是在本地按顺序翻转许多位,模拟激光攻击。为了演示这一概念,我们在 Xilinx 7 系列器件中实现了这一概念。

在基于SRAM的FPGA中,存储在SRAM存储器中的配置容易受到单个或多个事件扰动的影响,这些事件可能会改变器件用户编程的电路,例如改变设计组合逻辑或信号路由。这些干扰既可以来自自然来源,如宇宙辐射,也可能来自攻击源,如电磁扰动或激光故障攻击。

在基于SRAM的FPGA中,实现了不同的故障检测机制,旨在检测对安全敏感设计的激光故障攻击。据推测,经典的容错技术,如错误检测代码、模块化复制和三重复制,即使不应用于实现安全敏感功能的功能单元,也具有潜在的故障攻击检测机制,足以将任何异常情况作为警报传播到安全监督逻辑,以便可以激活进一步的缓解机制。

SRAM Security and Vulnerability To Hardware Trojan: Design Considerations

探讨了静态随机存取存储器(SRAM)中发现的不同模块的漏洞,包括核心单元、检测放大器、复制逻辑和硬件木马的时序单元。我们详细讨论了SRAM的设计和布局,以探讨如何利用自由死区进行硬件木马插入。SRAM块包含一些可能的稀有信号,可用于触发故意插入的特洛伊木马。数据模式和地址序列与常规测试不可能的数据背景相结合,可以产生罕见的触发条件。

攻击者可以发现并尝试利用这些漏洞引入硬件特洛伊木马并篡改嵌入式存储器中的数据完整性。由于SRAM在当今SoC中占据了最大的空间,因此其可靠性对SoC的整体性能起着关键作用。此外,SRAM使用最小几何形状的器件来增加密度,这使它们成为对缺陷最敏感的部件[2]。

我们展示了在SRAM电路的设计过程中,对手有几次机会进行恶意修改或插入。研究了BIST架构以探索可用于绕过工业测试时方法的漏洞。我们探索了几个自由的死区来安装特洛伊木马电路,并讨论了特洛伊木马插入(功能和参数硬件特洛伊木马)的可行性。我们还实现了一个硬件原型,展示了如何通过操纵SRAM模块的比较器信号来篡改SRAM模块的时序。然而,精心设计的运行时方法,包括侧信道分析和功能测试,可以检测到这些特洛伊木马。

转载请注明来源,欢迎对文章中的引用来源进行考证,欢迎指出任何有错误或不够清晰的表达,可以在下面评论区评论